# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

H01L 25/075 (2006.01) H01L 23/538 (2006.01) **H01L 27/12** (2006.01)

(52) CPC특허분류 **H01L 25/0753** (2013.01)

H01L 23/5386 (2013.01) (21) 출원번호 10-2019-0075904

(22) 출원일자 2019년06월25일 심사청구일자 2019년08월30일

(30) 우선권주장

1020180077668 2018년07월04일 대한민국(KR)

(11) 공개번호 10-2020-0004751

(43) 공개일자 2020년01월14일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

장경운

경기도 수원시 영통구 삼성로 129(매탄동)

박원순

경기도 수원시 영통구 삼성로 129(매탄동)

(뒷면에 계속)

(74) 대리인

정홍식, 김태헌

전체 청구항 수 : 총 14 항

## (54) 발명의 명칭 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치

### (57) 요 약

디스플레이 모듈이 개시된다. 개시된 디스플레이 모듈은 박막 트랜지스터 글래스 기판, 박막 트랜지스터 글래스 기판의 일면에 배열된 다수의 마이크로 엘이디 및 박막 트랜지스터 글래스 기판의 일면과 일면의 반대면을 각각 전기적으로 연결하도록 박막 트랜지스터 글래스 기판의 에지부에 형성된 다수의 측면 배선을 포함할 수 있다.

## 대 표 도 - 도1a

(52) CPC특허분류

**H01L 27/1214** (2013.01)

(72) 발명자

손동명

경기도 수원시 영통구 삼성로 129(매탄동)

신상민

경기도 수원시 영통구 삼성로 129(매탄동)

이창준

경기도 수원시 영통구 삼성로 129(매탄동)

정영기

경기도 수원시 영통구 삼성로 129(매탄동)

### 조성필

경기도 수원시 영통구 삼성로 129(매탄동)

허균

경기도 수원시 영통구 삼성로 129(매탄동)

홍순민

경기도 수원시 영통구 삼성로 129(매탄동)

### 명세서

## 청구범위

#### 청구항 1

박막 트랜지스터 글래스 기판;

상기 박막 트랜지스터 글래스 기판의 일면에 배열된 다수의 마이크로 엘이디; 및

상기 박막 트랜지스터 글래스 기판의 일면과 상기 일면의 반대면을 각각 전기적으로 연결하도록 상기 박막 트랜 지스터 글래스 기판의 에지부에 형성된 다수의 측면 배선;을 포함하는 디스플레이 패널.

### 청구항 2

제1항에 있어서,

상기 다수의 측면 배선은 각각,

상기 박막 트랜지스터 글래스 기판의 일면, 측단면 및 타면으로 이어지도록 형성된 디스플레이 패널.

### 청구항 3

제2항에 있어서.

상기 다수의 측면 배선은 각각,

양단이 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 제1 및 제2 접속 패드에 전기적으로 상호 연결된 디스플레이 패널.

### 청구항 4

제1항에 있어서.

상기 박막 트랜지스터 글래스 기판의 에지부는 상기 박막 트랜지스터 글래스 기판에서 상기 다수의 마이크로 엘이디가 배치된 액티브 영역을 제외한 더미 영역에 대응하는 디스플레이 패널.

### 청구항 5

제4항에 있어서,

상기 박막 트랜지스터 글래스 기판의 에지부는 상기 박막 트랜지스터 글래스 기판의 최외곽을 포함하거나, 상기 박막 트랜지스터 글래스 기판의 최외곽으로부터 상기 액티브 영역까지 이르는 영역을 포함하는 디스플레이 패널.

### 청구항 6

제1항에 있어서,

상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면에 간격을 두고 형성된 디스플레이 패널.

### 청구항 7

제6항에 있어서,

상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면에 형성된 다수의 요홈에 도포된 디스플레이 패널.

### 청구항 8

제7항에 있어서,

상기 다수의 측면 배선은 표면이 상기 박막 트랜지스터 글래스 기판의 측단면과 동일 측면에 위치한 디스플레이패널.

### 청구항 9

제7항에 있어서,

상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면보다 내측으로 형성된 디스플레이 패널.

### 청구항 10

제6항에 있어서,

상기 다수의 측면 배선은 각각.

양단이 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 다수의 제1 및 제2 접속 패드에 전기적으로 상호 연결된 디스플레이 패널.

#### 청구항 11

제10항에 있어서,

상기 제1 및 제2 접속 패드는 각 측면 배선의 양단을 덮는 디스플레이 패널.

#### 청구항 12

제1항에 있어서,

상기 박막 트랜지스터 기판의 에지부에는 다수의 측면 배선의 덮는 보호층이 형성된 디스플레이 패널.

#### 청구항 13

제12항에 있어서,

상기 보호층은 절연재질로 이루어지는 디스플레이 패널.

### 청구항 14

다수의 디스플레이 패널이 연속적으로 연결된 대형 디스플레이 장치에 있어서,

상기 각 디스플레이 패널은, 박막 트랜지스터 글래스 기판;

상기 박막 트랜지스터 글래스 기판의 일면에 배열된 다수의 마이크로 엘이디; 및

상기 박막 트랜지스터 글래스 기판의 일면과 상기 일면의 반대면을 각각 전기적으로 연결하도록 상기 박막 트랜 지스터 글래스 기판의 에지부에 형성된 다수의 측면 배선;을 포함하고,

상기 마이크로 엘이디는 3개 당 하나의 픽셀을 이루며,

상기 각 디스플레이 패널에 구비된 복수의 픽셀은 동일한 제1 피치로 배치되고, 상기 디스플레이 패널의 픽셀들 중 서로 인접한 디스플레이 패널들의 픽셀들은 상기 제1 피치와 동일한 제2 피치로 배치되는 대형 디스플레이 장치.

### 발명의 설명

### 기술분야

[0001]

본 개시는 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치에 관한 것으로, 보다 상세하게는, 구동 회로의 본당 영역을 TFT 기판의 후면으로 이동하기 위해 TFT 기판의 에지부에 측면 배선 구조를 배치함으로써 베젤리스를 구현하는 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치에 관한 것이다.

### 배경기술

- [0002] 디스플레이 장치는 픽셀 또는 서브 픽셀 단위로 동작이 되면서 다양한 색을 표현하고 있으며, 각각의 픽셀 또는 서브 픽셀 TFT(Thin Film Transistor)에 의해 동작이 제어된다. 복수의 TFT 는 연성 가능한 기판, 글래스 기판 또는 플라스틱 기판에 배열되며, 이를 TFT 기판이라고 한다.

- [0003] 이와 같은 TFT 기판은 플렉서블(flexible) 디바이스, 작은 사이즈로 웨어러블 디바이스(예를 들면, Wearable Watch 등)에서부터 큰 사이즈로 수십인치에 이르는 TV까지 디스플레이를 구동하는 기판으로써 활용되고 있다. TFT 기판을 구동하기 위해서는 TFT 기판에 전류를 가할 수 있는 외부 회로(External IC) 또는 구동 회로(Driver IC)와 연결한다. 일반적으로 TFT 기판과 각 회로는 COG(Chip on Glass) 본딩이나 FOG(Film on Glass) 본딩 등을 통해 연결된다. 이러한 연결을 위해서는 TFT 기판의 가장자리에 일정한 면적을 가지는 영역 즉, 베젤 영역 (bezel area)이 확보되어야 한다.

- [0004] 최근 들어 디스플레이 패널에서 영상이 표시되는 영역 즉, 액티브 영역(Active area)을 최대화할 수 있도록 베젤 영역을 줄이거나 없앤 베젤 리스(bezel-less) 기술에 대한 연구 및 개발이 꾸준히 진행되고 있으며, 일환으로 US9,367,094(공개일: 2016.06.14)에 개시된 디스플레이 패널이 있다. 현재 일부 스마트폰과 같은 소형 디스플레이 장치나 TV, 전광판과 같은 대형 디스플레이 장치에는 베젤 리스 디스플레이 패널이 적용되고 있다.

## 발명의 내용

### 해결하려는 과제

- [0005] 본 개시의 목적은, TFT 기판의 베젤 영역을 최소화하기 위해 TFT 기판의 에지부에 측면 배선을 형성하여 구동 회로(Driver IC)의 본딩 영역을 TFT 기판의 후면(rear surface)으로 배치함으로써 베젤 리스를 실현할 수 있는 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치를 제공하는데 있다.

- [0006] 또한, 본 개시의 다른 목적은,  $\mu$ -LED를 이용한 디스플레이 장치에 있어서, 복수의  $\mu$ -LED를 TFT 기판에 실장함에 있어서  $\mu$ -LED 실장 면의 외측에서 TFT 기판과 구동 회로를 연결하는 측면 배선을 배치하여  $\mu$ -LED의 실장 조밀도가 증가된 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치를 제공하는데 있다.

- [0007] 또한, 본 개시의 또 다른 목적은, 베젤 리스를 구현한 디스플레이 패널을 다수 연결하여 제작하는 대형 디스플레이(LFD: Large Format Display) 장치의 경우 서로 인접한 디스플레이 패널의 최외곽 픽셀 간의 피치를 단일 디스플레이 패널의 피치와 동일하게 유지할 수 있도록 하여 각 디스플레이 패널 사이의 심(seam)이 나타나는 것을 미연에 방지할 수 있는 디스플레이 패널 및 이를 이용한 대형 디스플레이 장치를 제공하는데 있다.

### 과제의 해결 수단

- [0008] 상기 목적을 달성하기 위한 본 개시의 일 실시 예에 따른 디스플레이 패널은, 박막 트랜지스터 글래스 기판; 상기 박막 트랜지스터 글래스 기판의 일면에 배열된 다수의 마이크로 엘이디; 및 상기 박막 트랜지스터 글래스 기판의 일면과 상기 일면의 반대면을 각각 전기적으로 연결하도록 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 다수의 측면 배선;을 포함하는 디스플레이 패널을 제공한다.

- [0009] 상기 다수의 측면 배선은 각각, 상기 박막 트랜지스터 글래스 기판의 일면, 측단면 및 타면으로 이어지도록 형성될 수 있다.

- [0010] 상기 다수의 측면 배선은 각각, 양단이 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 제1 및 제2 접속 패드에 전기적으로 상호 연결될 수 있다.

- [0011] 상기 박막 트랜지스터 글래스 기판의 에지부는 상기 박막 트랜지스터 글래스 기판에서 상기 다수의 마이크로 엘이디가 배치된 액티브 영역을 제외한 더미 영역에 대응할 수 있다.

- [0012] 상기 박막 트랜지스터 글래스 기판의 에지부는 상기 박막 트랜지스터 글래스 기판의 최외곽을 포함하거나, 상기 박막 트랜지스터 글래스 기판의 최외곽으로부터 상기 액티브 영역까지 이르는 영역을 포함할 수 있다.

- [0013] 상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면에 간격을 두고 형성될 수 있다. 이 경우, 상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면에 형성된 다수의 요홈에 도포될 수 있다.

- [0014] 상기 다수의 측면 배선은 표면이 상기 박막 트랜지스터 글래스 기판의 측단면과 동일 측면에 위치할 수 있다.

- [0015] 상기 다수의 측면 배선은 상기 박막 트랜지스터 글래스 기판의 측단면보다 내측으로 형성될 수 있다.

- [0016] 상기 다수의 측면 배선은 각각, 양단이 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 제1 및 제2 접속 패드에 전기적으로 상호 연결될 수 있다. 이 경우, 상기 제1 및 제2 접속 패드는 각 측면 배선의 양단을 덮도록 형성될 수 있다.

- [0017] 상기 박막 트랜지스터 기판의 에지부에는 다수의 측면 배선의 덮는 보호층이 형성될 수 있다. 이 경우, 상기 보호층은 절연재질로 이루어질 수 있다.

- [0018] 또한, 본 개시에 따른 다수의 디스플레이 패널이 연속적으로 연결된 대형 디스플레이 장치는 상기 각 디스플레이 패널은, 박막 트랜지스터 글래스 기판; 상기 박막 트랜지스터 글래스 기판의 일면에 배열된 다수의 마이크로 엘이디; 및 상기 박막 트랜지스터 글래스 기판의 일면과 상기 일면의 반대면을 각각 전기적으로 연결하도록 상기 박막 트랜지스터 글래스 기판의 에지부에 형성된 다수의 측면 배선을 포함하고, 상기 마이크로 엘이디는 3개당 하나의 픽셀을 이루며, 상기 각 디스플레이 패널에 구비된 복수의 픽셀은 동일한 제1 피치로 배치되고, 상기 디스플레이 패널의 픽셀들 중 서로 인접한 디스플레이 패널들의 픽셀들은 상기 제1 피치와 동일한 제2 피치로 배치될 수 있다.

### 발명의 효과

- [0019] 이상 설명한 바와 같이 본 개시의 다양한 실시 예에 따르면, TFT 기판의 전면과 후면을 전기적으로 연결하기 위한 배선을 TFT 기판의 에지부에 형성함으로써 TFT 기판에서의 더미 영역을 최소화할 수 있어 베젤 리스 디스플 레이 패널을 용이하게 구현할 수 있다.

- [0020] 또한, 베젤 리스 디스플레이 패널을 다수 연결하여 대형 디스플레이 장치를 형성하는 경우, 각 디스플레이 패널 이 연결되는 부분에 심(seam)이 나타나지 않아 디스플레이 품질을 향상시킬 수 있다.

### 도면의 간단한 설명

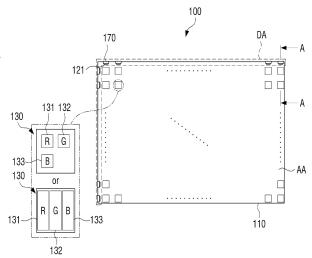

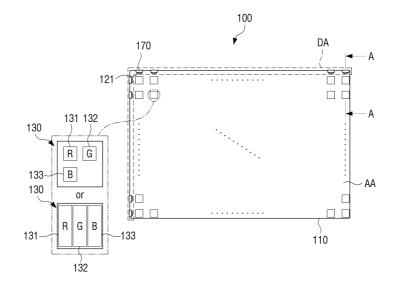

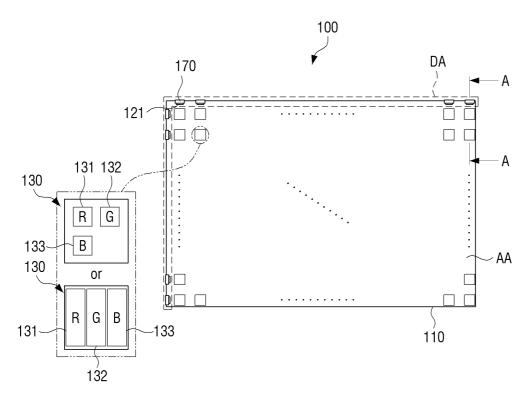

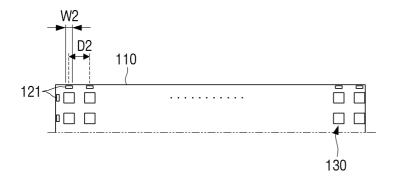

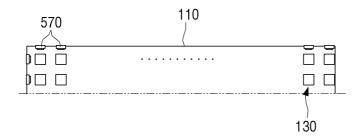

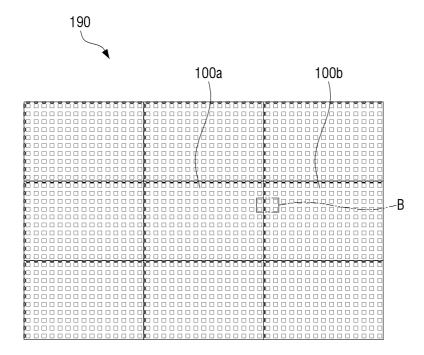

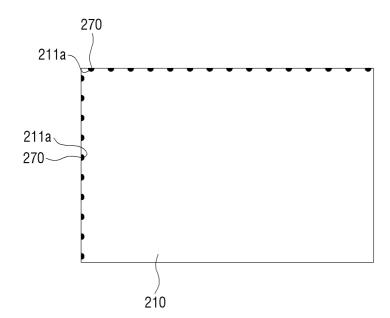

- [0021] 도 1a는 본 개시의 일 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

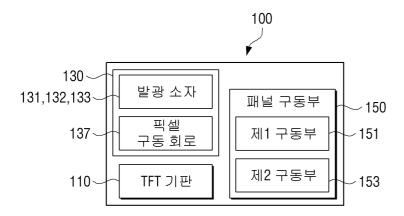

- 도 1b는 본 개시의 일 실시예에 따른 디스플레이 패널을 나타내는 블록도이다.

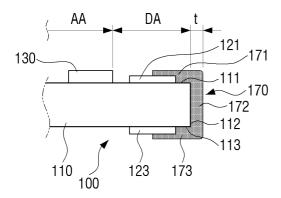

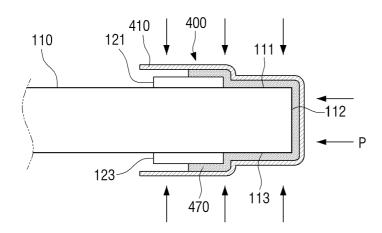

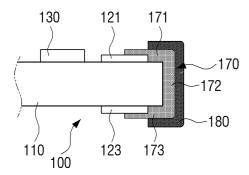

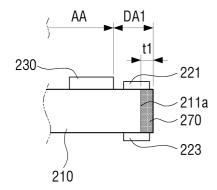

- 도 2는 도 1a에 표시된 A-A 선을 따라 나타낸 단면도이다.

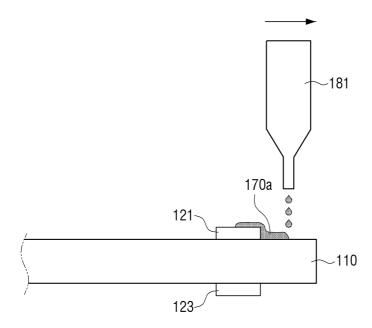

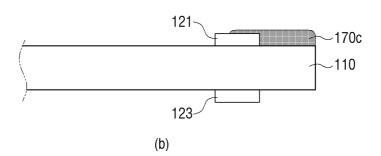

- 도 3은 잉크 젯 방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

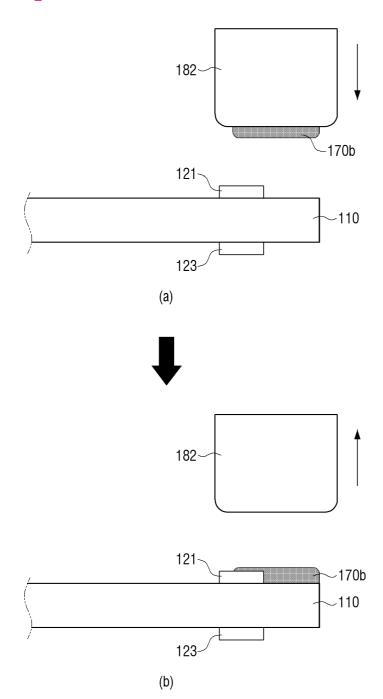

- 도 4는 스탬핑 방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

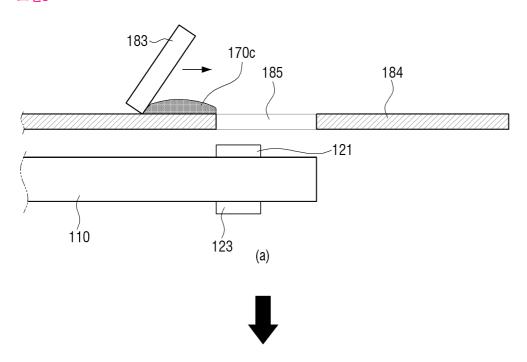

- 도 5는 스크린 인쇄 방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- 도 6은 금속 증착 방법을 통해 TFT 기판의 에지부에 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- 도 7a는 접착부재를 나타낸 상면도이다.

- 도 7b는 다수의 측면 배선이 형성되지 않은 TFT 기판을 나타낸 개략도이다.

- 도 7c는 접착 방법을 통해 TFT 기판의 에지부에 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- 도 7d는 테이프를 제거하는 상태를 나타낸 개략도이다.

- 도 8a는 TFT 기판의 에지부에 도전층이 형성된 것을 나타낸 개략도이다.

- 도 8b는 도전층 상에 마스킹부재가 형성된 것을 나타낸 개략도이다.

- 도 8c는 다수의 측면 배선이 형성된 TFT 기판의 에지부를 나타낸 개략도이다.

- 도 9a는 본 개시의 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

- 도 9b는 본 개시의 또 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

- 도 9c는 본 개시의 또 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

- 도 10은 본 개시의 일 실시예에 따른 디스플레이 패널을 다수 연결하여 형성된 대형 디스플레이 장치를 나타내

- 는 정면도이다.

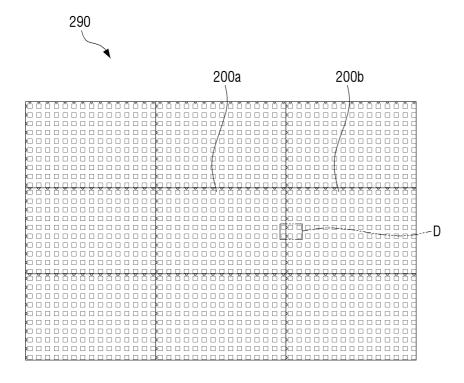

- 도 11은 도 10에 표시된 B 부분을 나타내는 확대도이다.

- 도 12는 TFT 기판의 에지부에 형성된 측면 배선을 보호하도록 측면 배선에 보호층을 적층한 단면도이다.

- 도 13은 본 개시의 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

- 도 14는 도 13에 표시된 C-C 선을 따라 나타낸 단면도이다.

- 도 15 내지 도 18은 본 개시의 다른 실시예에 따른 디스플레이 패널의 제조 공정을 순차적으로 나타내는 도면들이다.

- 도 19는 본 개시의 다른 실시예에 따른 디스플레이 패널을 다수 연결하여 형성된 대형 디스플레이 장치를 나타내는 정면도이다.

- 도 20은 도 19에 표시된 D 부분을 나타내는 확대도이다.

- 도 21은 본 개시의 또 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이다.

- 도 22는 도 21에 표시된 E-E 선을 따라 나타낸 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0022] 본 개시를 설명함에 있어, 관련된 공지 기술에 대한 구체적인 설명이 본 개시의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명을 생략한다. 또한, 동일한 구성의 중복 설명은 되도록 생략하기로 한다.

- [0023] 이하의 설명에서 사용되는 구성요소에 대한 접미사 "부"는 명세서 작성의 용이함만이 고려되어 부여되거나 혼용되는 것으로서, 그 자체로 서로 구별되는 의미 또는 역할을 갖는 것은 아니다.

- [0024] 본 개시에서 사용한 용어는 실시 예를 설명하기 위해 사용된 것으로, 본 개시를 제한 및/또는 한정하려는 의도 가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 다수의 표현을 포함한다.

- [0025] 본 개시에서, '포함하다' 또는 '가지다' 등의 용어는 명세서상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0026] 본 개시에서 사용된 "제1," "제2," "첫째," 또는 "둘째," 등의 표현들은 다양한 구성요소들을, 순서 및/또는 중요도에 상관없이 수식할 수 있고, 한 구성요소를 다른 구성요소와 구분하기 위해 사용될 뿐 해당 구성요소들을 한정하지 않는다.

- [0027] 어떤 구성요소(예: 제1 구성요소)가 다른 구성요소(예: 제2 구성요소)에 "(기능적으로 또는 통신적으로) 연결되어((operatively or communicatively) coupled with/to)" 있다거나 "접속되어(connected to)" 있다고 언급된 때에는, 상기 어떤 구성요소가 상기 다른 구성요소에 직접적으로 연결되거나, 다른 구성요소(예: 제3 구성요소)를 통하여 연결될 수 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소(예: 제1 구성요소)가 다른 구성요소(예: 제2 구성요소)에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 상기 어떤 구성요소 소와 상기 다른 구성요소 사이에 다른 구성요소(예: 제 3 구성요소)가 존재하지 않는 것으로 이해될 수 있다.

- [0028] 본 개시의 실시예들에 따른 디스플레이 패널은 TFT 글래스 기판(이하, 'TFT 기판'이라 함)의 에지부에 측면 배선을 형성하여 TFT 기판의 전면(front surface)에 배열된 다수의 발광소자와 TFT 기판의 후면(back surface)에 배치되는 회로들을 전기적으로 연결할 수 있다. 여기서, TFT 기판은 기판(글래스 기판, 연성 기판 또는 플라스틱 기판)과 기판의 일면에 형성된 복수의 TFT로 이루어질 수 있으며, 백플레인(backplane)으로 칭할 수 있다.

- [0029] 여기서, TFT 기판의 에지부는 TFT 기판의 최외곽일 수 있다. 또한 TFT 기판의 에지부는 TFT 기판의 최외곽으로 부터 영상이 디스플레이 되는 액티브 영역(active area)까지 이르는 더미 영역(dummy area)일 수 있다. 따라서 더미 영역(dummy area)은 TFT 기판의 측단면(side end surface)과, 측단면에 인접한 TFT 기판의 전면 일부 및 후면 일부를 포함할 수 있다.

- [0030] 여기서, 발광소자는 μ-LED(micro Light Emitting Diode)일 수 있으며, 이 경우 각 μ-LED는 R 서브 픽셀(Red color sub-pixel), G 서브 픽셀(Green color sub-pixel), B 서브 픽셀(Blue color sub-pixel)을 이룬다. 단일

픽셀(pixel)은 3개의 R, G, B 서브 픽셀로 이루어질 수 있으며, TFT 기판의 각각의 TFT는 서브 픽셀 단위로 형성된다.

- [0031]  $\mu$ -LED는 스스로 발광하므로 백라이트 유닛, 액정층, 편광자를 생략할 수 있고 최상층에 얇은 글래스 층이 배치될 수 있다. 따라서  $\mu$ -LED는 OLED보다 더 얇은 두께로 형성될 수 있다.

- [0032] 또한, μ-LED는 무기물질을 이용하므로 번인 현상이 발생하지 않고 유기물질을 이용한 OLED보다 발광효율이 약 3배 높고 전력 소모는 절반 정도에 그친다. 이에 따라 μ-LED가 실장된 디스플레이 패널을 스마트폰에 적용하면 화면을 밝은 곳에서도 더 뚜렷하게 볼 수 있고 배터리 사용 시간도 길어진다.

- [0033] 또한, μ-LED는 롤러 전사방식을 통해 곡률이 있는 기판에도 실장할 수 있고 고무처럼 잘 늘어나는 기판 위에서 도 소자를 붙일 수 있어 자유자재로 형태가 바뀌는 투명 디스플레이의 제작도 가능해지므로 실질적으로 실장할 수 있는 기판에 제약이 없다.

- [0034] 또한, μ-LED는 크기가 100um 이하의 초소형으로 제작되며 소형 웨어러블 기기(스마트 시계 등)에 적용 시 초고 해상도를 구현할 수 있다. 전술한 바와 같이 초고해상도를 구현할 수 있는 μ-LED는 전환 시간(색상을 완전히 바꾸는데 걸리는 시간)이 나노 초 단위이므로 VR(Virtual Reality) 및 AR(Augmented Reality) 헤드셋에 적용시 영상 품질을 극대화할 수 있다.

- [0035] 또한, TFT 기판의 에지부에 형성되는 측면 배선은 TFT 기판의 전면에 형성된 제1 접속 패드와 TFT 기판의 후면에 형성된 제2 접속 패드를 전기적으로 연결할 수 있다. 이를 위해 측면 배선은 TFT 기판의 전면, 측단면 및 후면을 따라 형성되며 일단이 제1 접속 패드에 전기적으로 연결되고 타단이 제2 접속 패드에 전기적으로 연결될수 있다. 이때, 측면 배선은 일부분이 TFT 기판의 측단면 위에 형성되므로 측면 배선의 두께만큼 TFT 기판의 측단면보다 돌출 될 수 있다.

- [0036] 또한, TFT 기판의 에지부에 형성되는 측면 배선은 TFT 기판의 측단면보다 돌출되지 않도록 TFT 기판의 측단면으로부터 TFT 기판의 내측 방향으로 형성될 수도 있다. 이를 위해 TFT 기판의 측단면을 지나는 측면 배선의 일부분은 TFT 기판의 측단면에 형성된 요홈에 형성될 수 있다. 이 경우 측면 배선의 일부분은 요홈을 완전히 메우거나 요홈의 내주면을 따라 소정 두께로 코팅될 수 있다. 측면 배선의 일부분이 요홈을 완전히 메우는 경우, 측면 배선의 일부분의 표면은 TFT 기판의 측단면과 동일한 면에 위치할 수 있다. 또한 측면 배선의 일부분이 요홈의 내주면을 따라 소정 두께로 코팅되는 경우, 측면 배선의 일부분의 표면은 TFT 기판의 측단면보다 TFT 기판의 내측으로 위치할 수 있다.

- [0037] 이와 같이 본 개시의 실시예들에 따른 디스플레이 패널은 TFT 기판의 전면에서 더미 영역을 최소화하고 액티브 영역을 최대화함으로써 베젤 리스를 구현할 수 있다.

- [0038] 이처럼 본 개시의 베젤 리스를 구현하기 위한 구조하에서는 더미 영역이 감소되므로 상대적으로 액티브 영역이 증가할 수 있다. 따라서 단위 디스플레이 패널에 대한 µ-LED의 실장 조밀도가 증가될 수 있다.

- [0039] 이와 같이 베젤 리스가 구현된 디스플레이 패널을 다수를 연결하는 경우, 액티브 영역을 최대화할 수 있는 대형 디스플레이(LFD) 장치를 제공할 수 있다. 이 경우 각 디스플레이 패널은 더미 영역을 최소화함에 따라 서로 인접한 디스플레이 패널의 각 픽셀들 간의 피치를 단일 디스플레이 패널 내의 각 픽셀들 간의 피치와 동일하게 유지하도록 형성할 수 있다. 이에 따라 각 디스플레이 패널 사이의 연결부분에서 심(seam)이 나타나는 것을 방지할 수 있다.

- [0040] 이하에서 첨부된 도면을 참조하여 본 개시의 다양한 실시 예를 상세히 설명한다.

- [0041] 도 1a는 본 개시의 일 실시예에 따른 디스플레이 패널을 나타내는 정면도이고, 도 1b는 본 개시의 일 실시예에 따른 디스플레이 패널을 나타내는 블록도이며, 도 2는 도 1에 표시된 A-A 선을 따라 나타낸 단면도이다.

- [0042] 본 개시의 일 실시예에 따른 디스플레이 패널(100)은 다수의 픽셀 구동 회로(137)가 형성된 TFT 기판(110)과, TFT 기판의 일면(이하, 'TFT 기판의 전면(front surface)'이라 함)에 배열된 다수의 픽셀(130)과, 제어신호를 생성하고 생성된 제어 신호를 TFT 기판에 형성된 각 픽셀 구동 회로(137)로 제공하는 패널 구동부(150)와, TFT 기판(110)의 에지부에 형성되어 픽셀 구동 회로(137)와 패널 구동부(150)를 전기적으로 연결하는 측면 배선 (170)을 포함할 수 있다.

- [0043] 도 1 내지 도 2를 참조하면, TFT 기판(110)은 TFT 기판의 전면(111)에 배열된 다수의 픽셀(130)을 제어하기 위해 가로로 배치된 다수의 데이터 신호 라인과 세로로 배치된 다수의 게이트 신호 라인이 형성될 수 있다.

- [0044] TFT 기판의 전면(111)은 다수의 픽셀(130)을 통해 영상을 디스플레이할 수 있는 영역인 액티브 영역(AA: Active Area)과, 액티브 영역을 제외한 나머지 영역인 더미 영역(DA: Dummy Area)으로 나누어질 수 있다. 이 경우 더미 영역(DA)은 TFT 기판(110)의 에지부에 대응할 수 있으며, 본 개시에서는 더미 영역(DA)과 TFT 기판(110)의 에지부를 동일한 구성으로 취급한다.

- [0045] 도 1a를 참조하면, 다수의 픽셀(130)은 TFT 기판(110)의 전면에 매트릭스 형태로 배열될 수 있다. 각 픽셀(13 0)은 Red, Green, Blue 컬러에 해당하는 3개의 R, G, B 서브 픽셀(131,132,133)을 포함할 수 있다. 각 서브 픽셀(131,132,133)은 해당 서브 픽셀의 색상을 발광하는 μ-LED(micro Light Emitting Diode)로 이루어질 수 있다. 본 개시에서는 '서브 픽셀'과 'μ-LED'를 동일한 구성으로 취급한다.

- [0046] R, G, B 서브 픽셀(131,132,133)은 하나의 픽셀(130) 내에서 매트릭스 형태로 배열되거나, 순차적으로 배열될수 있다. 다만, 이러한 서브 픽셀의 배치 형태는 일 예이며, R, G, B 서브 픽셀(131,132,133)은 각 단일 픽셀(130) 내에서 다양한 형태로 배치될 수 있다. 각 단일 픽셀(130)은 각각 R, G, B 서브 픽셀(131,132,133)에 대응하는 μ-LED를 구동하기 위한 픽셀 구동 회로를 포함할 수 있다.

- [0047] 한편, 본 개시에서 하나의 픽셀(130)은 R, G, B 서브 픽셀(131,132,133)을 각각 구동하기 위한 3개의 픽셀 구동 회로(137)를 포함하는 것으로 정의할 수도 있다.

- [0048] 패널 구동부(150)는 COG(Chip on Class) 본딩 또는 FOG(Film on Glass) 본딩 방식으로 TFT 기판(110)에 연결될 수 있다. 이와 같은 패널 구동부(150)는 다수의 픽셀 구동 회로(137)를 구동하여 다수의 픽셀 구동 회로(137) 각각에 전기적으로 연결된 다수의  $\mu$ -LED(131,132,133)의 발광을 제어할 수 있다. 특히, 패널 구동부(150)는 제 1 구동부(151)와 제2 구동부(153)를 통해 다수의 픽셀 구동 회로를 라인별로 제어할 수 있다.

- [0049] 제1 구동부(131)는 TFT 기판의 전면(111)에 형성된 다수의 가로 라인들을 영상 프레임당 하나의 라인씩 순차적으로 제어하기 위한 제어 신호를 생성하고, 생성된 제어 신호를 해당 라인에 각각 연결된 픽셀 구동 회로에 전송할 수 있다.

- [0050] 아울러, 제1 구동부(131)는 게이트 드라이버(gate driver)로 지칭될 수 있다.

- [0051] 제2 구동부(153)는 TFT 기판의 전면(111)에 형성된 다수의 세로라인들을 영상 프레임당 하나의 라인씩 순차적으로 제어하기 위한 제어 신호를 생성하고, 생성된 제어 신호를 해당 라인에 연결된 각각 연결된 픽셀 구동 회로 (137)로 전송할 수 있다.

- [0052] 아울러, 제2 구동부(153)는 데이터 드라이버(data driver)로 지칭될 수 있다.측면 배선(170)은 TFT 기판(110)의 에지부를 따라 소정 간격을 두고 다수로 형성될 수 있다.

- [0053] 측면 배선(170)은 TFT 기판의 전면(111)에 형성된 제1 접속 패드(121)와 TFT 기판의 후면(113)에 형성된 제2 접속 패드(123)를 전기적으로 연결할 수 있다.

- [0054] 이 경우, 제1 접속 패드(121)는 TFT 기판의 전면(111) 상측과 TFT 기판의 전면(111) 좌측을 따라 소정 간격을 두고 다수 형성될 수 있다. TFT 기판의 전면(111) 상측을 따라 배열된 다수의 제1 접속 패드들(121)은 게이트 신호 배선과 전기적으로 연결될 수 있고, TFT 기판의 전면(111) 좌측을 따라 배열된 다수의 제1 접속 패드들 (121)은 데이터 신호 배선과 전기적으로 연결될 수 있다.

- [0055] 측면 배선(170)은 TFT 기판의 전면(111)의 제1 접속 패드(121)와 TFT 기판의 후면(113)의 제2 접속 패드(123)를 상호 전기적으로 연결하도록, 일단이 전면 패드에 전기적으로 연결되고 타단이 후면 패드에 전기적으로 연결될 수 있다.

- [0056] 구체적으로, 도 2와 같이, 측면 배선(170)은 TFT 기판(110)의 에지부에서 TFT 기판의 전면(111)에 형성된 제1 부분(171)과, TFT 기판의 측단면(112)에 형성된 제2 부분(172)과, TFT 기판의 후면(113)에 형성된 제3 부분 (173)을 포함할 수 있다. 이 경우, 측면 배선(170)은 제2 부분(172)이 TFT 기판의 측단면(112) 상에 형성되므로 TFT 기판의 측단면(112)으로부터 측면 배선(170)의 두께(t)만큼 돌출될 수 있다.

- [0057] 이와 같이 TFT 기판의 측단면(112)에 돌출된 상태로 형성된 측면 배선(170)의 제2 부분(172)의 단선을 방지하기 위해, 측면 배선(170) 위에 별도의 보호층(180, 도 12 참조)을 적층하는 것도 물론 가능하다. 보호층(180)의 두 께는 측면 배선(170)의 두께와 같거나 작은 두께로 형성할 수 있다.

- [0058] 이와 같은 측면 배선(170)은 도 3 내지 도 8c에 도시된 바와 같이 다양한 공정을 통해 TFT 기판(110)의 에지부에 형성될 수 있다. 도 3 내지 도 8c에는 설명의 편의를 위해 TFT 기판(110)에 배치된 다수의 픽셀(130)을 생략

한다.

- [0059] 도 3은 잉크 젯 방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- [0060] 도 3을 참조하면, TFT 기판(110)의 에지부에 잉크 형태의 도전성 금속물질(170a)를 분사하는 잉크 젯 방식으로 측면 배선이 형성될 수 있다. 이 경우 도전성 금속물질(170a)은 TFT 기판(170)의 에지부의 전면, 측단면 및 후면에 순차적으로 도포됨에 따라 측면 배선을 형성할 수 있다.

- [0061] 도 4는 스탬핑 방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- [0062] 도 4를 참조하면, 승강 가능한 가동부재(182)를 통해 페이스트(paste) 형태의 도전성 금속물질(170b)를 TFT 기판(110)의 에지부에 도포할 수 있다. 이 경우에도 도전성 금속물질(170b)은 TFT 기판(170)의 에지부의 전면, 측단면 및 후면에 순차적으로 도포됨에 따라 측면 배선을 형성할 수 있다.

- [0063] 도 5는 스크린 인쇄방법을 통해 TFT 기판의 에지부에 도전성 금속물질을 도포하여 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- [0064] 도 5를 참조하면, TFT 기판(110)의 상측에 마스크(184)를 배치하되, 마스크에 형성된 배출구멍(185)을 측면 배선이 형성된 위치인 TFT 기판(110)의 에지부에 대응하도록 배치한다. 이어서 마스크(184)의 상면에 준비된 페이스트 형태의 도전성 금속물질(170c)을 스크레이퍼(183)로 밀어서 배출구멍(185)을 통해 TFT 기판(110)의 에지부에 도포시킨다. 이 경우에도 도전성 금속물질(170c)은 TFT 기판(170)의 에지부의 전면, 측단면 및 후면에 순차적으로 도포됨에 따라 측면 배선을 형성할 수 있다.

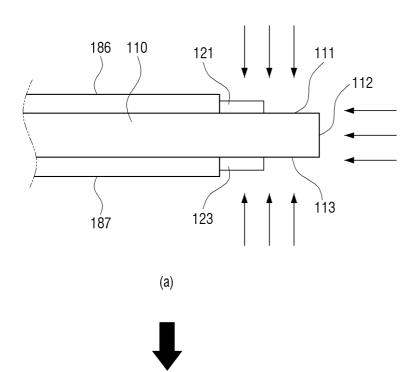

- [0065] 도 6은 금속 증착 방법을 통해 TFT 기판의 에지부에 측면 배선을 형성하는 공정을 나타내는 개략도이다.

- [0066] 도 6을 참조하면, 금속 증착 방법(예를 들면, 스퍼터링 증착 방법)을 통해 TFT 기판(110)의 에지부에 측면 배선 (170)을 형성할 수 있다. 이를 위해, TFT 기판(110)의 에지부가 노출되도록 테이프나 액상 수지를 이용한 마스크(186,187)를 TFT 기판(110)에 형성하고 도전성 금속물질을 증착한다. 이 경우, 금속 증착 설비에 따라, TFT 기판(170)의 에지부의 전면, 측단면 및 후면에 동시에 도전성 금속물질을 증착하거나 각 면에 순차적으로 증착할 수 있다.

- [0067] 이하에서는, 도 7a 내지 도 7d를 참조하여, 본 개시의 일 실시예에 따른 측면 배선(470)을 형성하는 접착 방법에 대해 설명한다.

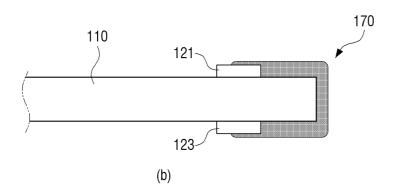

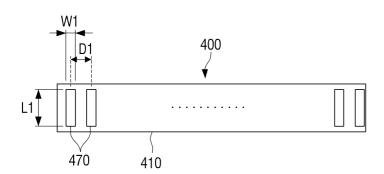

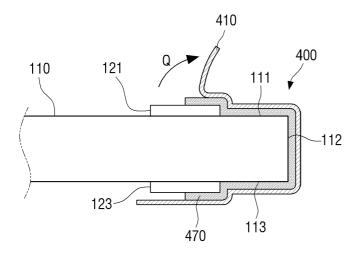

- [0068] 도 7a는 접착부재(400)를 나타낸 상면도이고, 도 7b는 다수의 측면 배선(470)이 형성되지 않은 TFT 기판(110)을 나타낸 개략도이며, 도 7c는 접착 방법을 통해 TFT 기판(110)의 에지부에 측면 배선(470)을 형성하는 공정을 나타내는 개략도이고, 도 7d는 테이프(410)를 제거하는 상태를 나타낸 개략도이다.

- [0069] 도 7a 및 도 7b를 참조할 때, 접착부재(400)는 테이프(410) 및 테이프(410) 상에 형성된 다수의 도전성 부재 (470)를 포함할 수 있다.

- [0070] 테이프(410)는 일면에 배치되는 다수의 도전성 부재(470)와 접착할 수 있는 재질로 형성될 수 있다. 아울러, 테이프(410)는 열을 받을 경우 접착성을 잃어버리는 재질로 구성될 수 있다.

- [0071] 이에 따라, 테이프(410)에 열을 가하는 경우, 다수의 도전성 부재(470)는 테이프(410)와 용이하게 분리될 수 있다.

- [0072] 다수의 도전성 부재(470, 또는 측면 배선)는 도전성을 가지는 물질로 구성될 수 있다. 아울러, TFT 기판(110)의 에지부에 부착되는 경우, 도전성 부재(470)는 제1 접속 패드(121)와 제2 접속 패드(123)를 전기적으로 연결하는 측면 배선을 형성할 수 있다.

- [0073] 여기서, 도전성 부재(470)는 TFT 기판(110)의 에지부에 접착 고정되기 전 상태를 의미하며, 측면 배선은 TFT 기판(110)의 에지부에 접착 고정되고 난 후의 상태를 의미할 수 있다.

- [0074] 도전성 부재(470) 각각은 제1 너비(W1)와 제1 길이(L1)를 가지는 사각형 형상일 수 있다.

- [0075] 여기서, 제1 너비(W1)는 제1 접속 패드(121)의 제2 너비(W2)와 대응될 수 있다. 예를 들어, 도전성 부재(470)의 제1 너비(W1)는 도전성 부재(470)와 전기적, 물리적으로 연결되는 제1 접속 패드(121)의 제2 너비(W2)를 고려하여 결정될 수 있다. 구체적으로, 제1 너비(W1)는 제2 너비(W2)와 같거나 클 수 있다. 즉, 도전성 부재(470)는

- 제1 접속 패드(121)의 일부를 둘러싸도록 커버할 수 있다.

- [0076] 아울러, 도전성 부재(470)의 제1 너비(W1)는 제1 접속 패드(121)뿐만 아니라, 제2 접속 패드(123)의 너비를 고려해서 결정될 수 있다.

- [0077] 아울러, 제1 길이(L1)는 TFT 기판(110)의 에지부를 둘러쌈과 동시에 제1 접속 패드(121) 및 제2 접촉 패드(12 3)를 연결시키는 길이일 수 있다.

- [0078] 예를 들어, 제1 길이(L1)은 제1 접속 패드(121)로부터 TFT 기판의 전면(111), TFT 기판의 측단면(112), TFT 기판의 후면(113)을 포함하는 제2 접속 패드(123)까지의 거리일 수 있다.

- [0079] 또한, 다수의 도전성 부재(470)는 테이프(410) 상에서 제1 간격(D1)으로 이격되어 배치될 수 있다. 여기서, 제1 간격(D1)은 다수의 도전성 부재(470)의 중심선 사이의 거리이며, 다수의 제1 접속 패드(121)의 중심선 사이의 거리인 제2 간격(D2)와 대응될 수 있다.

- [0080] 이에 따라, 하나의 도전성 부재(470)는 하나의 제1 접속 패드(121) 및 하나의 제1 접속 패드(121)와 마주보는 하나의 제2 접속 패드(123)를 연결시킬 수 있다.

- [0081] 다음으로, 도 7c에 도시된 바와 같이, 접착부재(400)는 TFT 기판(110)의 에지부에 접착될 수 있다. 여기서, 하나의 도전성 부재(470)는 하나의 제1 접속 패드(121), TFT 기판의 전면(111), TFT 기판의 측단면(112), TFT 기판의 후면(113) 및 제2 접속 패드(123)와 접촉할 수 있다.

- [0082] 이에 따라, 제1 접속 패드(121)와 제2 접속 패드(123)는 전기적으로 연결될 수 있다.

- [0083] 이후, 접착부재(400)가 TFT 기판(110)의 에지부에 접착된 상태에서 접착부재(400)에 대해 열 압착(P)을 가할 수 있다. 이에 따라, 다수의 도전성 부재(470)는 TFT 기판(110)의 에지부에 접착되어 고정될 수 있다.

- [0084] 이에 따라, 다수의 도전성 부재(470)는 TFT 기판(110)의 에지부에 접착되어 다수의 측면 배선을 형성할 수 있다.

- [0085] 다음으로, 도 7d에 도시된 바와 같이, 테이프(410)는 다수의 도전성 부재(470)로부터 제거될 수 있다.

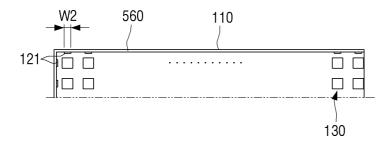

- [0086] 이하에서는, 도 8a 내지 도 8c를 참조하여, 본 개시의 일 실시예에 따른 측면 배선(570)을 형성하는 에칭 방법 에 대해 설명한다.

- [0087] 도 8a는 TFT 기판(110)의 에지부에 도전층(560, conductive layer)가 형성된 것을 나타낸 개략도이고, 도 8b는 도전층(560) 상에 마스킹부재(550)가 형성된 것을 나타낸 개략도이며, 도 8c는 다수의 측면 배선(570)이 형성된 TFT 기판(110)의 에지부를 나타낸 개략도이다.

- [0088] 먼저, 도 8a에 도시된 바와 같이, 도전층(560)는 TFT 기판(110)의 에지부를 따라 형성될 수 있다. 구체적으로, 도전층(560)는 제1 접속 패드(121), TFT 기판의 전면(111), TFT 기판의 측단면(112), TFT 기판의 후면(113) 및 제2 접속 패드(123)에 접착될 수 있다.

- [0089] 다음으로, 도 8b에 도시된 바와 같이, 다수의 제1 접속 패드(121) 및 다수의 제2 접속 패드(123)가 배치된 위치와 대응되도록, TFT 기판(110)의 에지부에 기 설정된 간격으로 마스킹부재(550)가 형성될 수 있다.

- [0090] 여기서, 마스킹부재(550)는 도전층(560)를 에칭하는 과정에서, 마스킹부재(550)가 형성된 영역에 배치된 도전층 (560)가 에칭되지 않도록 보호할 수 있다.

- [0091] 아울러, 마스킹부재(550)는 형성하고자 하는 다수의 측면 배선(570)의 형상과 대응될 수 있다. 예를 들어, 마스킹부재(550)의 제3 너비(W3)는 형성하고자 하는 다수의 측면 배선(570)의 너비와 대응될 수 있다.

- [0092] 또한, 제3 너비(W3)는 제1 접속 패드(121)의 제2 너비(W2)와 같거나 클 수 있다. 즉, 마스킹부재(550)는 제1 접속 패드(121)의 일부를 둘러싸도록 커버할 수 있다.

- [0093] 아울러, 마스킹부재(550)의 제3 너비(W3)는 제1 접속 패드(121)뿐만 아니라, 제2 접속 패드(123)의 너비를 고려해서 결정될 수 있다.

- [0094] 다음으로, 도 8b의 상태에서 도전층(560)에 대한 에칭 공정이 수행될 수 있다. 여기서, 에칭은 웨트 에칭(wet etching)과 드라이 에칭(dry etching)을 포함할 수 있다.

- [0095] 예를 들어, 마스킹부재(550)가 형성된 영역에 배치된 도전층(560)는 에칭되지 않으며, 마스킹부재(550)가 형성

- 되지 않은 영역에 배치된 도전층(560)는 에칭될 수 있다.

- [0096] 이에 따라, 도 8c에 도시된 바와 같이, 제1 접속 패드(121) 및 제2 접속 패드(123)가 배치된 위치와 대응되도록 다수의 측면 배선(570)이 형성될 수 있다.

- [0097] 즉, 다수의 측면 배선(570)은 제1 접속 패드(121)와 제2 접속 패드(123)를 전기적, 물리적으로 연결시킬 수 있다.

- [0098] 이하에서는, 도 9a 내지 도 9c를 참조하여, 본 개시의 또 다른 실시예에 따른 다양한 디스플레이 패널(101, 102, 103)에 대해 설명한다.

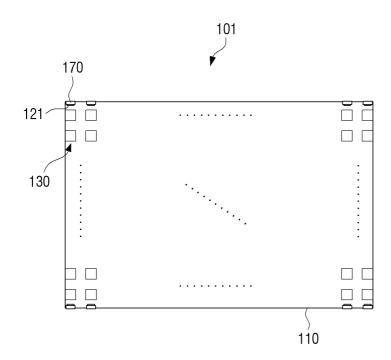

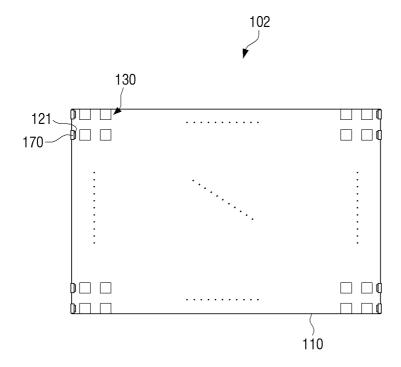

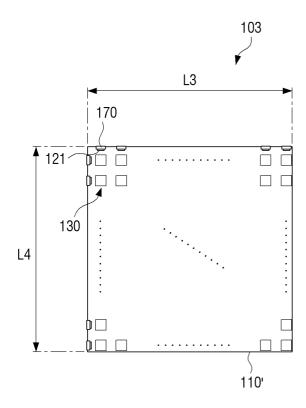

- [0099] 도 9a는 본 개시의 다른 실시예에 따른 디스플레이 패널(101)을 나타내는 정면도이고, 도 9b는 본 개시의 또 다른 실시예에 따른 디스플레이 패널(102)을 나타내는 정면도이며, 도 9c는 본 개시의 또 다른 실시예에 따른 디스플레이 패널(103)을 나타내는 정면도이다.

- [0100] 다수의 측면 배선(170)은 TFT 기판(110)의 4변 중 적어도 2변 이상에 형성될 수 있다. 여기서, 2변은 서로 다른 변을 의미할 수 있다.

- [0101] 예를 들어, TFT 기판(110)의 4변 중 하나의 변은 제1 구동부(131)의 신호를 전달 받기 위한 제1 접속 패드(121) 및 제2 접속 패드(123)가 배치될 수 있으며, TFT 기판(110)의 4변 중 나머지 하나의 변은 제2 구동부(153)의 신호의 전달을 받기 위한 제1 접속 패드(121) 및 제2 접속 패드(123)가 배치될 수 있다.

- [0102] 즉, 다수의 픽셀(130)을 구동하기 위해, TFT 기판(110)의 4변 중 한 변은 게이트 신호를 전달하기 위한 측면 배선(170)이 형성되고, TFT 기판(110)의 4변 중 다른 한 변은 데이터 신호를 전달하기 위한 측면 배선(170)이 형성될 수 있다.

- [0103] 예를 들어, 도 9a에 도시된 와 같이, 다수의 측면 배선(170) 및 다수의 측면 배선(170)이 연결시키는 제1 접속 패드(121)와 제2 접속 패드(123)는 TFT 기판(110)의 상측변 및 하측변에 형성될 수 있다.

- [0104] 또한, 도 9b에 도시된 바와 같이, 다수의 측면 배선(170) 및 다수의 측면 배선(170)이 연결시키는 제1 접속 패드(121)와 제2 접속 패드(123)는 TFT 기판(110)의 좌측변 및 우측변에 형성될 수 있다.

- [0105] 아울러, 도 9c에 도시된 바와 같이, 디스플레이 모듈(103)이 포함하는 TFT 기판(110`)은 도 1a에 도시된 직사각 형 형상의 디스플레이 모듈(100)의 TFT 기판(110)과 달리, 정사각형 형상일 수 있다.

- [0106] 예를 들어, TFT 기판(110`)의 네 측변의 길이는 모두 동일 할 수 있다. 구체적으로, 상측변의 제3 길이(L3)와 좌측변의 제4 길이(L4)는 동일할 수 있다.

- [0107] 이에 따라, 정사각형 형상의 또 다른 디스플레이 모듈(103)의 TFT 기판(110`)을 순차적으로 배치함에 따라, 다양한 크기의 고휘도, 고색감을 가지는 디스플레이 화면을 구현할 수 있다.

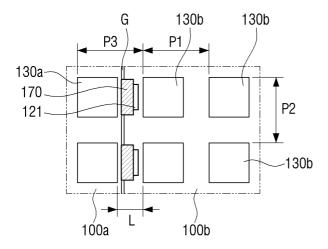

- [0108] 도 10은 본 개시의 일 실시예에 따른 디스플레이 패널을 다수 연결하여 형성된 대형 디스플레이 장치를 나타내는 정면도이고, 도 11은 도 10에 표시된 B 부분을 나타내는 확대도이다.

- [0109] 도 10을 참조하면, 상기에서와 같이 베젤 리스를 구현할 수 있는 본 개시의 일 실시예에 따른 디스플레이 패널 (100)은 다수를 연결하여 대형 디스플레이 장치(190)를 형성할 수 있다.

- [0110] 도 11을 참조하면, 대형 디스플레이 장치(190)를 이루는 서로 인접한 디스플레이 패널(100a, 100b)의 픽셀들은 서로 동일한 피치(P1, P2, P3)로 배치될 수 있다. 구체적으로, 제1 디스플레이 패널(100a)의 픽셀(130a)과 이에 인접한 제2 디스플레이 패널(100b)의 픽셀(130b)의 피치(P3)는 제2 디스플레이 패널(100b) 내의 픽셀들(130b)의 피치(P1, P2)와 동일하게 형성될 수 있다.

- [0111] 이와 같이 각 디스플레이 패널의 픽셀들의 피치와 제1 및 제2 디스플레이 패널(100a,100b)의 각 픽셀 (130a,130b)의 피치를 동일하게 하도록, 제1 디스플레이 패널(100a)의 픽셀(130a)의 일단으로부터 제2 디스플레이 패널(100b)의 픽셀에 일단까지의 거리(L)를 적절히 조절할 수 있다.

- [0112] 한편, 연결 부재(170)의 두께로 인해 서로 인접한 제1 및 제2 디스플레이 패널(100a,100b) 사이에 소정의 갭(G)이 형성될 수 있으나, 각 픽셀들의 피치가 동일하므로 대형 디스플레이 장치(190)에서 디스플레이되는 영상을 볼 때 각 디스플레이 패널의 연결부분에서 갭(G)으로 인한 심(seam)을 육안으로 확인하기 어렵다. 따라서, 베젤 리스가 구현된 디스플레이 패널(100)을 다수 연결하여 형성된 대형 디스플레이 장치(190)는 단일 디스플레

- 이 패널로 이루어진 것과 같은 효과를 얻을 수 있다.

- [0113] 전술한 디스플레이 패널(100)은 다수의 측면 배선(170)이 도 1과 같이 TFT 기판(110)의 상측과 좌측에 형성된 것으로 설명하였으나 이제 제한되지 않고, 다수의 측면 배선(170)은 TFT 기판(110)의 4변 중 1변 이상에 형성될 수 있다.

- [0114] 예를 들면, 다수의 측면 배선(170)은 TFT 기판(110)의 상측변과 하측변에 형성될 수도 있고, TFT 기판(110)의 상측변과 우측변에 형성될 수도 있고, TFT 기판(110)의 좌측변과 우측변에 형성될 수도 있고, TFT 기판(110)의 4변 중 3변에만 형성되는 등 다양한 위치에 형성될 수 있다.

- [0115] 도 12는 TFT 기판의 에지부에 형성된 측면 배선을 보호하도록 측면 배선에 보호층을 적층한 단면도이다.

- [0116] 또한, 디스플레이 패널을 다수 연결하여 대형 디스플레이 장치를 제작하는 경우, 다수의 측면 배선(170)이 TFT 기판(110)의 4변 중 1변 이상에 형성될 때 다수의 측면 배선의 형성 위치에 따라 서로 인접한 디스플레이 패널들의 측면 배선들이 쇼트될 수도 있다. 예를 들면, 다수의 측면 배선(170)이 TFT 기판(110)의 상측과 하측면에 형성된 디스플레이 패널을 다수 연결하는 경우, 상하로 인접한 디스플레이 패널의 측면 배선들이 쇼트될 수 있다.

- [0117] 이를 방지하기 위해, 도 12와 같이 다수의 측면 배선(170)을 덮어주는 보호층(180)을 형성하는 것이 바람직하다. 이러한 보호층(180)은 절연 기능과 함께 외부로부터 다수의 측면 배선(170)에 가해지는 물리적인 힘이나 충격에 의해 다수의 측면 배선(170)이 파손되는 것을 방지하는 보호 기능도 수행할 수 있다.

- [0118] 도 12에서는 보호층(180)은 측면 배선(170)의 제2 부분(172)을 완전히 덮고 제1 및 제3 부분(171,173)의 일부를 덮고 있으나, 이에 제한되지 않고 제1 내지 제3 부분(171,172,173) 전체를 덮도록 형성하는 것도 물론 가능하다. 보호층(180)은 하기에서 도 15 내지 도 18을 참조하여 설명하는 측면 배선(170)을 형성하기 위한 잉크 젯 방법, 스팸핑 방법, 증착 방법 등의 다양한 방법을 통해 형성할 수 있다.

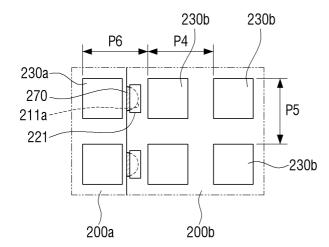

- [0119] 하기에서는 도 13 및 도 14를 참조하여 본 개시의 다른 실시예에 따른 디스플레이 패널(200)의 구조를 설명한다. 이 경우 디스플레이 패널(200)을 설명함에 있어 전술한 디스플레이 패널(100)과 동일한 구성에 대해서는 설명을 생략하고 상이한 구성인 측면 배선(270)을 중심으로 설명한다.

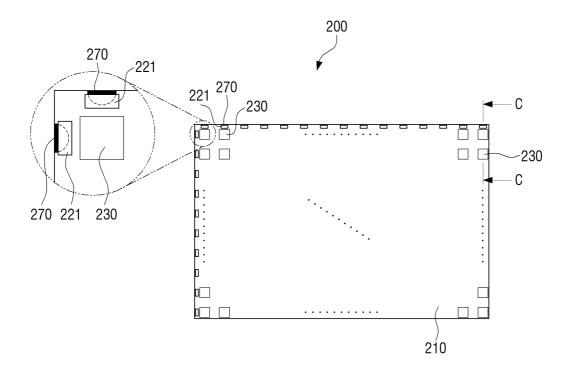

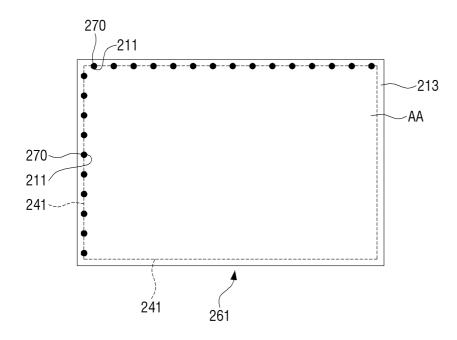

- [0120] 도 13은 본 개시의 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이고, 도 14는 도 13에 표시된 C-C 선을 따라 나타낸 단면도이다.

- [0121] 도 13을 참조하면, 디스플레이 패널(200)은 TFT 기판(210)의 전면에 매트릭스 형태로 다수의 픽셀(230)이 배열되며, TFT 기판(210)의 에지부에는 다수의 측면 배선(270)이 형성될 수 있다.

- [0122] 측면 배선(270)은 TFT 기판(210)의 측단면보다 돌출되지 않도록, TFT 기판(210)의 측단면보다 내측으로부터 TFT 기판(210)의 측단면과 대략 동일한 면까지의 두께를 가질 수 있다.

- [0123] 도 14를 참조하면, 측면 배선(270)이 TFT 기판(210)의 측단면보다 돌출되지 않도록 TFT 기판(210)의 측단면에 측면 배선(270)이 형성되는 요홈(211a)을 형성할 수 있다. 이 경우 측면 배선(270)에 전기적으로 연결되는 제1 및 제2 접속 패드(221,223)는 TFT 기판(210)의 전면 및 후면에 각각 형성될 수 있다.

- [0124] 제1 및 제2 접속 패드(221,223)는 각각 측면 배선(270)과의 전기적인 연결이 가능하도록 TFT 기판(210)에 측면 배선(270)이 형성된 후에 측면 배선(270)의 양단부를 덮을 수 있도록 TFT 기판(210)의 에지부에 형성될 수 있다.

- [0125] 이와 같이 측면 배선(270)이 TFT 기판(210)의 측단면보다 돌출되지 않도록 형성됨에 따라, 생산라인에서 TFT 기판(210)을 이송하거나 취급하는 중에 측면 배선(270)이 단선되는 것을 근본적으로 방지할 수 있다.

- [0126] 또한, 본 개시의 다른 실시예에 따른 디스플레이 패널(200)은 측면 배선(270)을 요홈(211a)에 삽입된 상태로 형성하고, 제1 및 제2 접속패턴(221,223)을 직접 연결함에 따라 TFT 기판(210)의 더미 영역(DA1)을 전술한 TFT 기판(110)의 더미 영역(DA)보다 더 축소된 상태로 형성할 수 있다.

- [0127] 한편, TFT 기판(210)의 에지부에 측면 배선(270)을 형성하기 위한 공정은 도 15 내지 도 18에 순차적으로 도시된다. 하지만, 측면 배선(270)을 형성하기 위한 공정은 이에 제한되지 않고 다양하게 공정을 통해 이루어질 수도 있다.

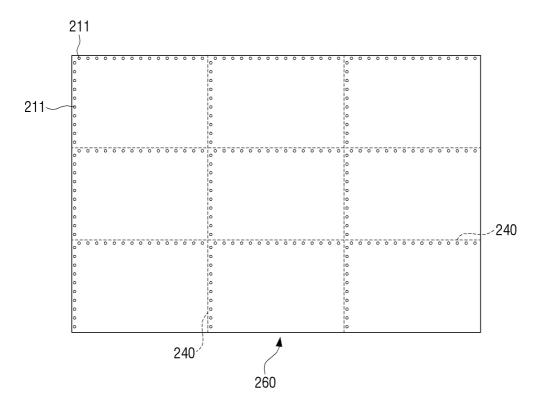

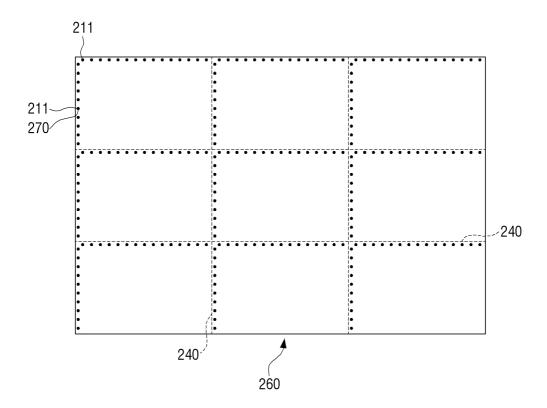

- [0128] 도 15 내지 도 18은 본 개시의 다른 실시에에 따른 디스플레이 패널의 제조 공정을 순차적으로 나타내는 도면들

이다.

- [0129] 도 15를 참조하면, 먼저 다수의 TFT 기판을 제작할 수 있는 정도의 대형 사이즈의 글래스(260)를 준비한다.

- [0130] 글래스(260)는 가상으로 구획된 다수의 영역에 리소그래피 공정을 통해 트랜지스터, 게이트 신호 라인, 데이터 신호 라인 등이 형성됨에 따라 TFT 기판으로 기능할 수 있다.

- [0131] 또한, 글래스(260)에서 가상으로 구획된 다수의 영역에 대응하도록 각각 다수의 홀(211)이 가공될 수 있다.

- [0132] 도 16을 참조하면, 다수의 홀(211)에 각각 도전성 금속물질을 도포한다. 이 경우 도전성 금속물질은 각 홀(21 1)을 완전히 메운 상태로 형성될 수 있다.

- [0133] 다수의 홀(211)에 도전성 금속물질을 모두 도포한 후 글래스(260)를 가상의 제1 커팅라인(240)을 따라 다수의 예비 TFT 기판(261)을 형성한다.

- [0134] 도 17을 참조하면, 각 예비 TFT 기판(261)의 에지부를 가상의 제2 커팅라인(241)을 따라 2차 커팅한다. 이 경우, 제2 커팅라인(241)은 일부분이 각 홀(211)의 중심을 지나가도록 설정될 수 있다. 따라서 2차 커팅을 통해 초소형의 홀(211)을 대략 반으로 커팅해야하므로, 2차 커팅은 1차 커팅보다 정밀한 가공으로 진행된다.

- [0135] 도 18을 참조하면, 각 홀(211)은 2차 커팅에 의해 대략 반원의 요홈(211a)으로 형성될 수 있다. 이어서 다수의  $\mu$ -LED가 전사(transfer) 기술 등의 다양한 공정을 통해 TFT 기판(210)에 실장될 수 있다.

- [0136] 도 19는 본 개시의 다른 실시예에 따른 디스플레이 패널을 다수 연결하여 형성된 대형 디스플레이 장치를 나타 내는 정면도이고, 도 20은 도 19에 표시된 D 부분을 나타내는 확대도이다.

- [0137] 이와 같이 구성된 디스플레이 패널(200)은 도 19와 같이 다수를 연결하여 대형 디스플레이 장치(290)로 형성될수 있다. 이 경우, 대형 디스플레이 장치(290)는 다수의 측면 배선(270)이 TFT 기판의 측단면보다 돌출되지 않도록 TFT 기판의 에지부에 형성됨에 따라 도 20과 같이 서로 인접한 디스플레이 패널(200a,200b) 사이에 갭(G)을 없앨 수 있다.

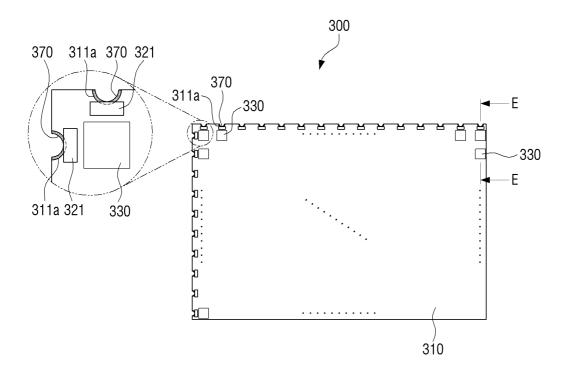

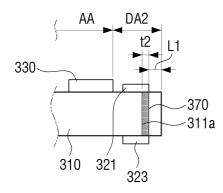

- [0138] 도 21은 본 개시의 또 다른 실시예에 따른 디스플레이 패널을 나타내는 정면도이고, 도 22은 도 21에 표시된 E-E 선을 따라 나타낸 단면도이다.

- [0139] 도 21을 참조하면, 본 개시의 또 다른 실시예에 따른 디스플레이 패널(300)은 전술한 본 개시의 다른 실시예에 따른 디스플레이 패널(200)과 대부분 동일한 구조를 가지며, 다만 측면 배선(370)의 두께 및 형상이 상이하게 형성될 수 있다.

- [0140] 측면 배선(370)은 디스플레이 패널(300)의 요홈(311a)의 내주면에 소정 두께를 갖도록 도포될 수 있다. 이와 같은 측면 배선(370)을 형성하기 위해, 글래스(260, 도 15 참조)에 형성된 각 홀(211, 도 15 참조)에 도전성 금속 물질을 완전히 메우지 않고 소정 두께를 갖도록 각 홀의 내주면에 도포한 후, 2차 커팅을 실시한다.

- [0141] 이에 따라, 측면 배선(370)은 도 21과 같이 대략 원호 형상으로 이루어질 수 있으며, 도 22와 같이 측면 배선 (370)의 일부분 표면은 TFT 기판(310)의 측단면보다 TFT 기판(310)의 내측에 위치할 수 있다.

- [0142] 도 22를 참조하면, TFT 기판(310)의 에지부의 전면 및 후면에는 각각 제1 및 제2 접속 패드(321,323)가 측면 배선(370)의 양단에 전기적으로 연결되도록 형성될 수 있다. 이 경우, 제1 및 제2 접속 패드(321,323)의 일부분은 각각 도 21과 같이 일부분이 측면 배선(370)의 양단의 일부분에만 접속되는 것으로 도시하였으나, 이에 제한되지 않고 제1 및 제2 접속 패드(321,323)는 배선(370)의 양단에 더 넓은 면적이 접속될 수 있다. 이를 위해, 제1 및 제2 접속 패드(321,323)는 도 21에 도시된 위치보다 TFT 기판(310)의 측단면에 더 가깝게 배치되도록 형성할수 있다.

- [0143] 또한, 본 개시의 또 다른 실시예에 따른 디스플레이 패널(300)은 TFT 기판(310)의 더미 영역(DA2)을 전술한 TFT 기판(110)의 더미 영역(DA)보다 더 축소된 상태로 형성할 수 있어 TFT 기판(110)의 액티브 영역을 넓힐 수 있다.

- [0144] 한편, 전술한 디스플레이 패널(200,300)에서는 다수의 측면 배선(270,370)이 도 13 및 도 21과 같이 TFT 기판 (210,310)의 상측과 좌측에 형성된 것으로 설명하였으나 이제 제한되지 않고, 다수의 측면 배선(270,370)은 TFT 기판(210,310)의 4변 중 1변 이상에 형성될 수 있다.

- [0145] 또한, 디스플레이 패널(200,300)을 다수 연결하여 대형 디스플레이 장치를 제작하는 경우, 디스플레이 패널 (100)과 마찬가지로 다수의 측면 배선(270,370))을 덮는 보호층을 형성할 수 있다. 이에 따라, 인접한 디스플레

이 패널들의 다수의 측면 배선(270,370) 간에 발생할 수 있는 쇼트와 외부로부터 다수의 측면 배선(270,370)에 가해지는 물리적인 힘이나 충격으로부터 다수의 측면 배선(270,370)을 보호할 수 있다.

- [0146] 이상 설명한 바와 같이 본 개시의 다양한 실시 예에 따르면, TFT 기판의 전면과 후면을 전기적으로 연결하기 위한 배선을 TFT 기판의 에지부에 형성함으로써 TFT 기판에서의 더미 영역을 최소화할 수 있어 베젤 리스 디스플 레이 패널을 용이하게 구현할 수 있다.

- [0147] 또한, 베젤 리스 디스플레이 패널을 다수 연결하여 대형 디스플레이 장치를 형성하는 경우, 각 디스플레이 패널 이 연결되는 부분에 심(seam)이 나타나지 않아 디스플레이 품질을 향상시킬 수 있다.

- [0148] 다양한 실시 예들에 따른 구성 요소(예: 모듈 또는 프로그램) 각각은 단수 또는 다수의 개체로 구성될 수 있으며, 전술한 해당 서브 구성 요소들 중 일부 서브 구성 요소가 생략되거나, 또는 다른 서브 구성 요소가 다양한 실시 예에 더 포함될 수 있다. 대체적으로 또는 추가적으로, 일부 구성 요소들(예: 모듈 또는 프로그램)은 하나의 개체로 통합되어, 통합되기 이전의 각각의 해당 구성 요소에 의해 수행되는 기능을 동일 또는 유사하게 수행할 수 있다. 다양한 실시 예들에 따른, 모듈, 프로그램 또는 다른 구성 요소에 의해 수행되는 동작들은 순차적, 병렬적, 반복적 또는 휴리스틱하게 실행되거나, 적어도 일부 동작이 다른 순서로 실행되거나, 생략되거나, 또는다른 동작이 추가될 수 있다.

- [0149] 이상의 설명은 본 개시의 기술 사상을 예시적으로 설명한 것에 불과한 것으로서, 본 개시가 속하는 기술 분야에 서 통상의 지식을 가진 자라면 본 개시의 본질적인 특성에서 벗어나지 않는 범위에서 다양한 수정 및 변형이 가능할 것이다. 또한, 본 개시에 따른 실시 예들은 본 개시의 기술 사상을 한정하기 위한 것이 아니라 설명하기한 것이고, 이러한 실시 예에 의하여 본 개시의 기술 사상의 범위가 한정되는 것은 아니다. 따라서, 본 개시의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 개시의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

### 부호의 설명

[0150] 110,210,310: TFT 기판

121,221,231: 제1 접속 패드

123,223,323: 제2 접속 패드

130,230,330: 픽셀

131,132,133: 서브 픽셀

170, 270, 370, 470, 570: 측면 배선

## 도면1a

## *도면1b*

# 도면7a

# *도면7b*

## *도면7c*

# 도면7d

# 도면8a

## 도면8b

# 도면8c

# 도면9a

## *도면9b*

## 도면9c

| 专利名称(译)        | 显示面板和使用该显示面板的大幅面                                           | 显示装置    |            |  |

|----------------|------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020200004751A                                           | 公开(公告)日 | 2020-01-14 |  |

| 申请号            | KR1020190075904                                            | 申请日     | 2019-06-25 |  |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                   |         |            |  |

| 申请(专利权)人(译)    | 三星电子有限公司                                                   |         |            |  |

| [标]发明人         | 장경운<br>박원순<br>손동명<br>신상민<br>이창준<br>정영기<br>조성필<br>허균<br>흥순민 |         |            |  |

| 发明人            | 장경운<br>박원순<br>손동명<br>신상민<br>이창준<br>정영기<br>조성필<br>허균<br>흥순민 |         |            |  |

| IPC分类号         | H01L25/075 H01L23/538 H01L27/1                             | 2       |            |  |

| CPC分类号         | H01L25/0753 H01L23/5386 H01L27                             | /1214   |            |  |

| 代理人(译)         | 정홍식<br>Gimtaeheon                                          |         |            |  |

| 优先权            | 1020180077668 2018-07-04 KR                                |         |            |  |

| 外部链接           | Espacenet                                                  |         |            |  |

|                |                                                            |         | 100        |  |

#### 摘要(译)

公开了一种显示模块。 公开的显示模块可以包括薄膜晶体管玻璃基板;和 多个微型LED布置在薄膜晶体管玻璃基板的一侧上; 多个侧面布线形成在薄膜晶体管玻璃基板的边缘部分上,以将薄膜晶体管玻璃基板的一侧与该一侧的相对侧电连接。 根据本发明,可以使虚设区域最小化。